# **Boundary-Scan Tutorial**

| See the ASSET homepage on the World Wide W | /eb | at |

|--------------------------------------------|-----|----|

| http://www.asset-intertech.com             |     |    |

ASSET, the ASSET logo and ScanWorks are registered trademarks, and DFT Analyzer is a trademark of ASSET InterTech, Inc.

Windows is a registered trademark of Microsoft Corporation.

© 2007-2011, ASSET InterTech, Inc. © 2007, R.G. Bennetts

# **Table of Contents**

| Introduction                                                                        | 5  |

|-------------------------------------------------------------------------------------|----|

| Chapter 1: The Motivation for Boundary-Scan Architecture                            | 6  |

| Chapter 2: The Principle of Boundary-Scan Architecture                              | 7  |

| Using the Scan Path                                                                 | 7  |

| Chapter 3: IEEE 1149.1 Device Architecture                                          | 11 |

| The Instruction Register                                                            | 11 |

| The Instructions                                                                    | 12 |

| Using the Instruction Register (IR)                                                 | 13 |

| Use of the "Capture 01" Mode                                                        |    |

| The Test Access Port (TAP)                                                          |    |

| The Bypass Register                                                                 |    |

| The Identification Register                                                         |    |

| Use of the lsb = 1 Feature                                                          |    |

| Boundary-Scan Register                                                              |    |

| Providing Boundary-Scan Cells                                                       |    |

| Accessing Other Core-Logic Registers                                                | 21 |

| Chapter 4: Application at the Board Level                                           |    |

| General Strategy                                                                    |    |

| Interconnect Test Example                                                           |    |

| Practical Aspects of Using Boundary-Scan Technology                                 | 24 |

| Handling Non-Boundary-Scan Clusters                                                 | 24 |

| Access to RAM Arrays Other Issues of Boundary Scan-to-Non-Boundary Scan Interfacing |    |

| Assembling the Final Test Program                                                   |    |

| Tester Hardware                                                                     |    |

|                                                                                     |    |

| Chapter 5: Related Data Formats                                                     | 29 |

| Boundary-Scan Description Language (BSDL)                                           | 29 |

| What is BSDL?                                                                       |    |

| How BSDL is Used                                                                    |    |

| Elements of BSDL                                                                    |    |

| Hierarchical Scan Description Language (HSDL)                                       |    |

| HSDL Module Statements                                                              |    |

| Serial Vector Format (SVF)                                                          |    |

| What Is SVF?                                                                        |    |

| SVF Structure                                                                       |    |

| Standard Test And Programming Language, STAPL                                       |    |

| What is STAPL?                                                                      | 36 |

| Basic Structure of a STAPL program                                                  | 36 |

| STAPL Composers, Players and Sessions                                               |    |

| STAPL Program Example                                                               |    |

| STAPL: final comments                                                               | 39 |

| Chapter 6: IEEE 1532 In-Circuit Configuration Standard                              | 40 |

| Development of the IEEE 1532 Standard                                               |    |

| PLD Programming Environment                                                         |    |

| PLD Programming Formats and Languages                                               |    |

| IEEE 1532 In-System Configuration Standard                                          | 43 |

| Accessing Program Data and Address Registers                                        |    |

| IEEE 1532 Instructions                                                              |    |

| Flows, Procedures and Actions                                                       |    |

| Conclusions                                                                         |    |

| To Probe Further                                                                    | 48 |

| Chapter 7: The IEEE 1149.6 Standard                                                 | 49 |

| What's The Problem?                                                                 |    |

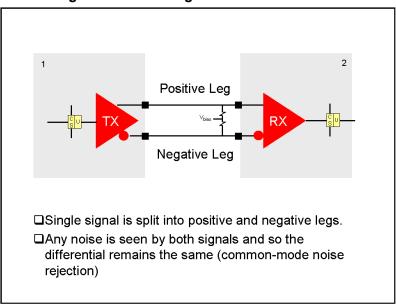

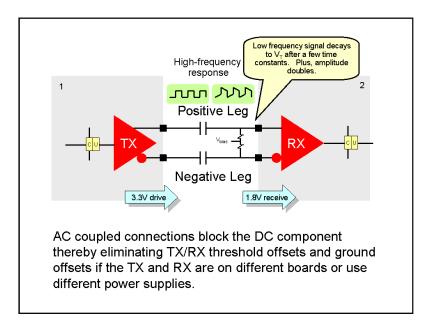

| DC and AC-coupled Low-Voltage Differential Signals                                  |    |

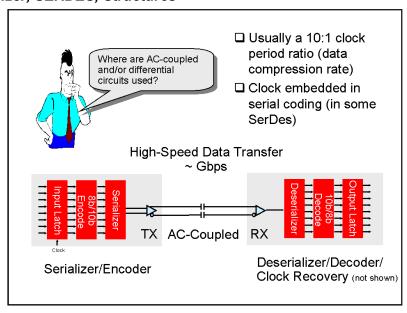

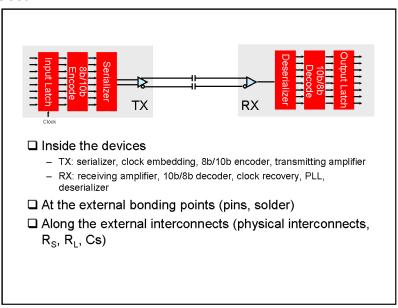

| SERializer-DESerializer, SERDES, Structures                                         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

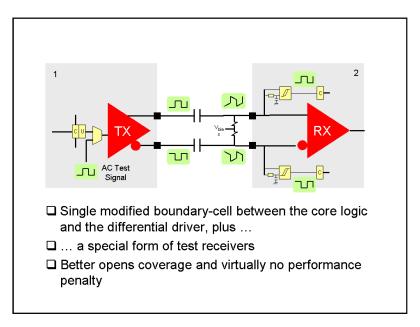

| Options for AC-Coupling Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| IEEE 1149.6 Basic Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| TO Flobe Fulfilei                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

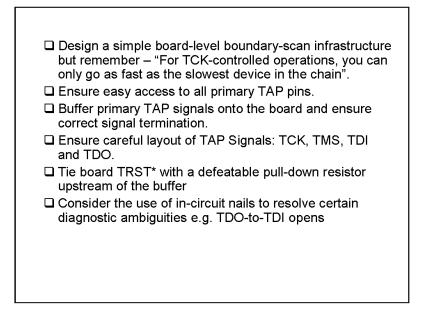

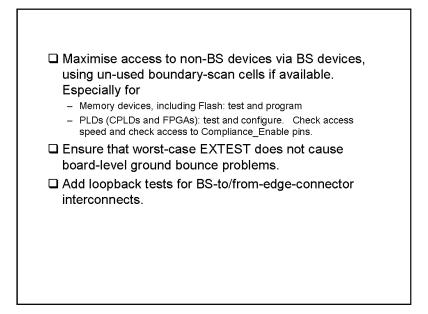

| Chapter 8: DFT Boundary-Scan Guidelines for Devices and Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57 |

| Why Do We Need DFT Guidelines?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

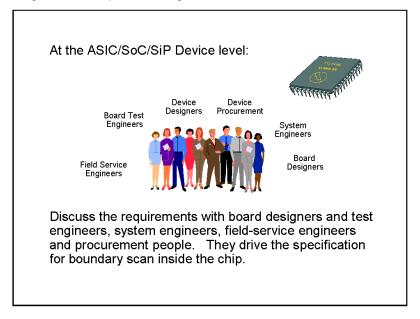

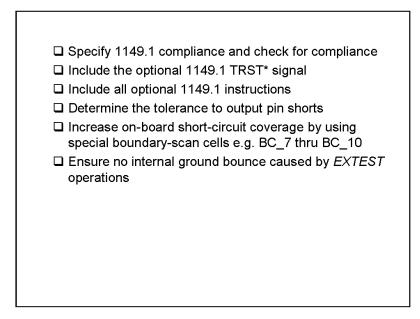

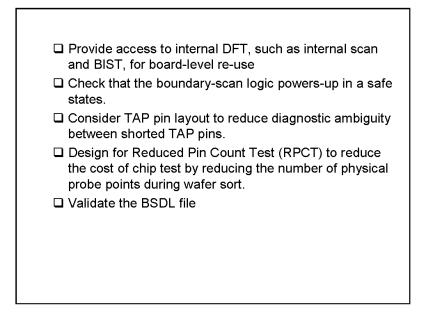

| Chip-Level DFT Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Board-Level DFT Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| To Probe Further                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62 |

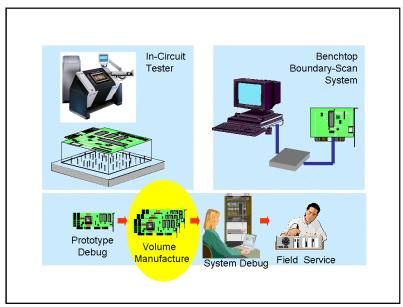

| Chapter 9: Boundary-Scan Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63 |

| Product Life Cycle Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Design Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63 |

| Manufacturing Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| Field Test and Repair  Boundary-Scan Tools Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| Design Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| Manufacturing Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| Field Test and Repair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

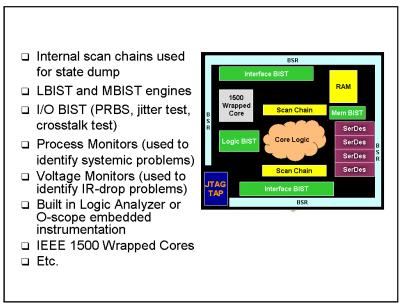

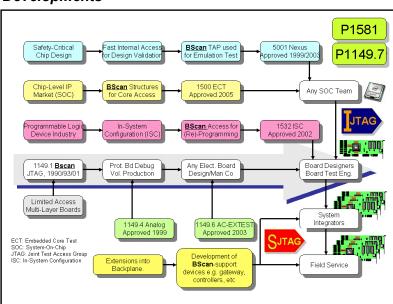

| Chapter 10: Recent Developments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| IEEE P1687 (IJTAG) Initiative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Boundary Scan and its Relationship with other Test Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Other New Standard Developments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Chapter 11: Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 75 |

| Zihliaaranhu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Reference  Table of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76 |

| Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

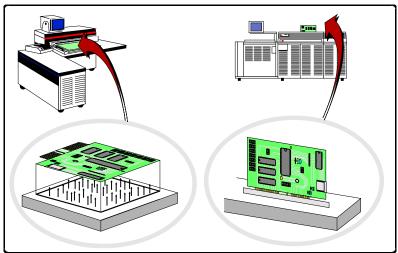

| Table of Figures  Figure 1: ICT versus Functional Test  Figure 2: Principle of Boundary-Scan Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Table of Figures  Figure 1: ICT versus Functional Test  Figure 2: Principle of Boundary-Scan Architecture  Figure 3: Using the Boundary-Scan Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| Table of Figures  Figure 1: ICT versus Functional Test  Figure 2: Principle of Boundary-Scan Architecture  Figure 3: Using the Boundary-Scan Path  Figure 4: Basic Boundary-Scan Cell.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test  Figure 2: Principle of Boundary-Scan Architecture  Figure 3: Using the Boundary-Scan Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| Table of Figures  Figure 1: ICT versus Functional Test  Figure 2: Principle of Boundary-Scan Architecture  Figure 3: Using the Boundary-Scan Path  Figure 4: Basic Boundary-Scan Cell.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

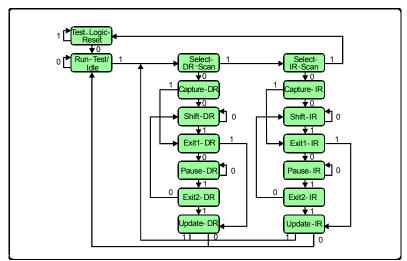

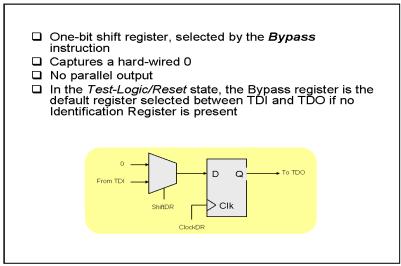

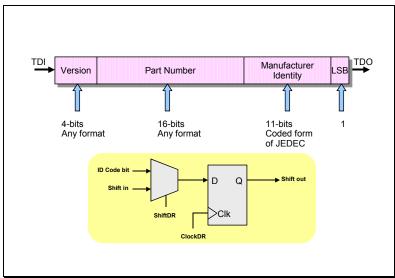

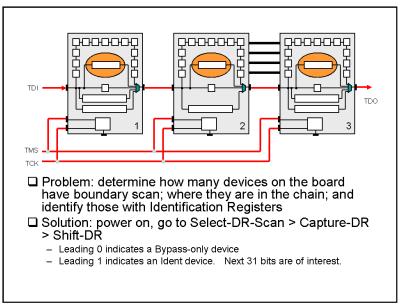

| Table of Figures  Figure 1: ICT versus Functional Test  Figure 2: Principle of Boundary-Scan Architecture  Figure 3: Using the Boundary-Scan Path  Figure 4: Basic Boundary-Scan Cell  Figure 5: Bed-of-Nails Fault Coverage  Figure 6: Boundary-Scan Fault Coverage (Intest)  Figure 7: Boundary-Scan Fault Coverage (Extest)  Figure 8: IEEE 1149.1 Chip Architecture  Figure 9: The Instruction Register  Figure 10: Using the Instruction Register — Step 1  Figure 11: Using the Instruction Register — Step 3  Figure 12: TAP Controller Global View  Figure 13: TAP Controller State Table Diagram  Figure 15: Device Identification Code Structure                                                                                                                                                                                                                                                                   |    |

| Table of Figures  Figure 1: ICT versus Functional Test  Figure 2: Principle of Boundary-Scan Architecture  Figure 3: Using the Boundary-Scan Path  Figure 4: Basic Boundary-Scan Cell  Figure 5: Bed-of-Nails Fault Coverage  Figure 6: Boundary-Scan Fault Coverage (Intest)  Figure 7: Boundary-Scan Fault Coverage (Extest)  Figure 8: IEEE 1149.1 Chip Architecture  Figure 9: The Instruction Register  Figure 10: Using the Instruction Register — Step 1  Figure 11: Using the Instruction Register — Step 3  Figure 12: TAP Controller Global View  Figure 13: TAP Controller State Table Diagram  Figure 15: Device Identification Code Structure  Figure 16: Use of the Isb = 1 Feature — Step 1                                                                                                                                                                                                                   |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Table of Figures  Figure 1: ICT versus Functional Test  Figure 2: Principle of Boundary-Scan Architecture  Figure 3: Using the Boundary-Scan Path  Figure 4: Basic Boundary-Scan Cell  Figure 5: Bed-of-Nails Fault Coverage  Figure 6: Boundary-Scan Fault Coverage (Intest)  Figure 7: Boundary-Scan Fault Coverage (Extest)  Figure 8: IEEE 1149.1 Chip Architecture  Figure 9: The Instruction Register  Figure 10: Using the Instruction Register — Step 1  Figure 11: Using the Instruction Register — Step 3  Figure 12: TAP Controller Global View  Figure 13: TAP Controller State Table Diagram  Figure 14: The Bypass Register  Figure 15: Device Identification Code Structure  Figure 16: Use of the Isb = 1 Feature — Step 1  Figure 17: Use of the Isb = 1 Feature — Step 3  Figure 18: Basic Boundary-Scan Cell (Input)  Figure 19: Basic Boundary-Scan Cell (Input)  Figure 20: A Reason for the Hold State |    |

| Table of Figures  Figure 1: ICT versus Functional Test.  Figure 2: Principle of Boundary-Scan Architecture.  Figure 3: Using the Boundary-Scan Path.  Figure 4: Basic Boundary-Scan Cell.  Figure 5: Bed-of-Nails Fault Coverage.  Figure 6: Boundary-Scan Fault Coverage (Intest).  Figure 7: Boundary-Scan Fault Coverage (Extest).  Figure 8: IEEE 1149.1 Chip Architecture.  Figure 9: The Instruction Register.  Figure 10: Using the Instruction Register — Step 1.  Figure 11: Using the Instruction Register — Step 3.  Figure 12: TAP Controller Global View.  Figure 13: TAP Controller State Table Diagram.  Figure 14: The Bypass Register.  Figure 15: Device Identification Code Structure.  Figure 16: Use of the Isb = 1 Feature — Step 1.  Figure 17: Use of the Isb = 1 Feature — Step 3.  Figure 18: Basic Boundary-Scan Cell (Input).  Figure 19: Basic Boundary-Scan Cell (Input)                       |    |

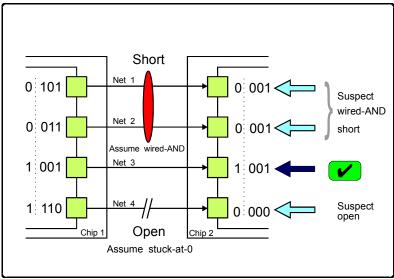

| Figure 23: | Interconnect Testing Example                            | 22 |

|------------|---------------------------------------------------------|----|

| Figure 24: | Interconnect Testing Solution                           | 23 |

| Figure 25: | Detecting the Fault                                     | 23 |

| Figure 26: | Locating the Fault                                      | 24 |

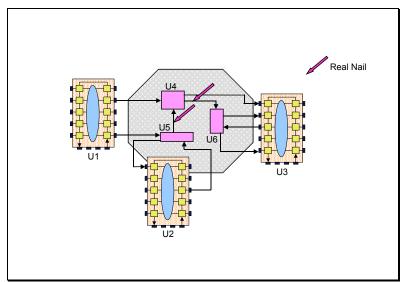

| Figure 27: | Handling Non-Boundary Scan Clusters                     | 25 |

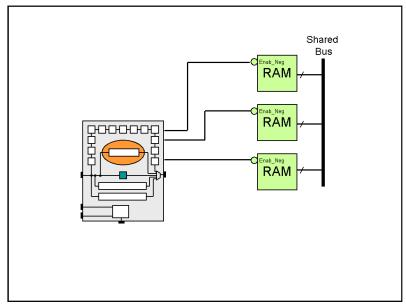

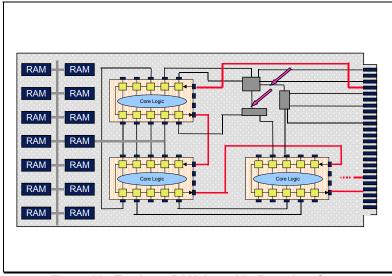

| Figure 28: | Testing a RAM Array Via Boundary Scan                   | 25 |

| Figure 29: | Boundary Scan-to-non-Boundary Scan Interface            | 26 |

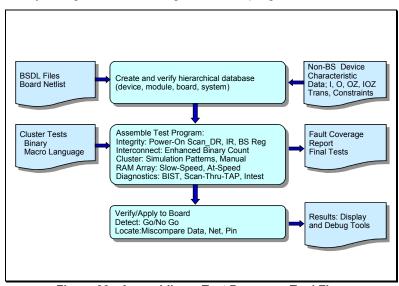

| Figure 30: | Assembling a Test Program - Tool Flow                   | 27 |

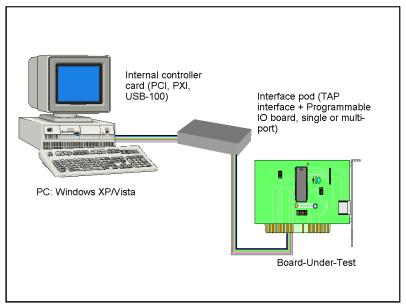

| Figure 31: | Tester Hardware                                         | 28 |

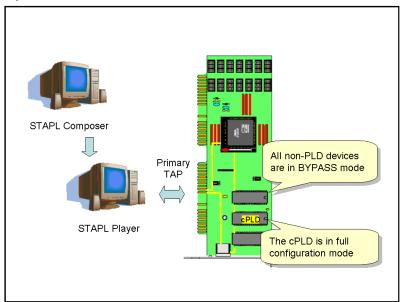

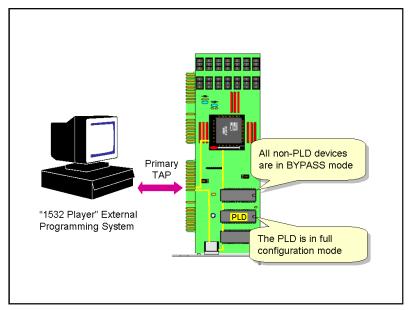

| Figure 32: | Programming a cPLD Through the Scan Chain               | 36 |

| Figure 33: | Background on In-System Configuration                   | 40 |

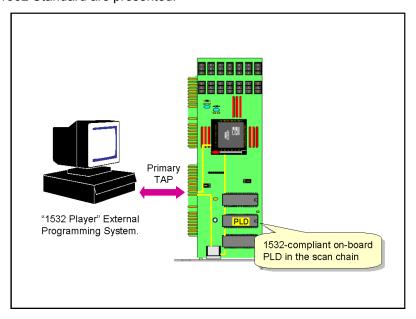

| Figure 34: | Programming the PLD Through the Scan Chain              | 41 |

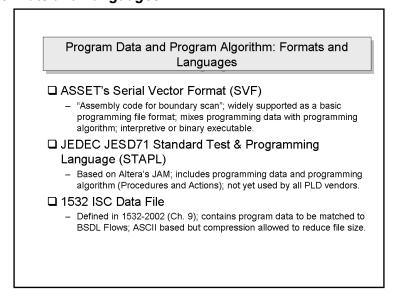

| Figure 35: | PLD Programming Formats and Languages                   | 42 |

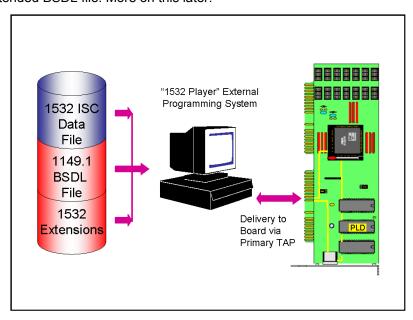

| Figure 36: | Getting Programming Data to the PLD                     | 42 |

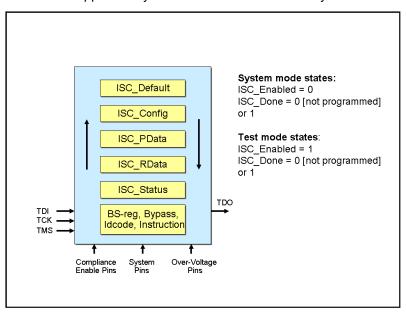

| Figure 37: | IEEE 1532 - General Architecture                        | 43 |

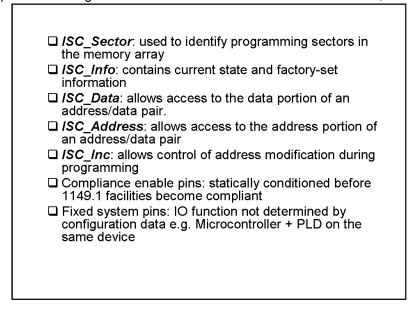

| Figure 38: | IEEE 1532 - New Registers                               | 44 |

| Figure 39: | IEEE 1532 - Other New Registers (Optional)              | 44 |

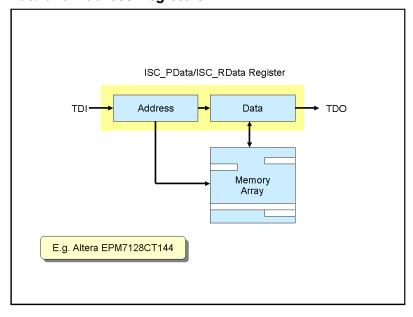

| Figure 40: | Basic Program Memory Array Access                       | 44 |

| Figure 41: | Mandatory Instructions                                  | 45 |

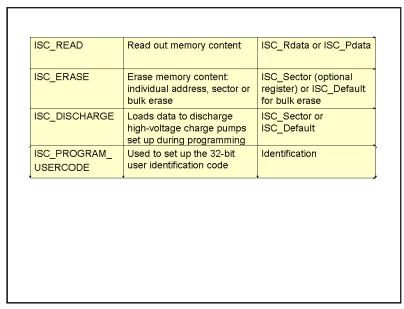

| Figure 42: | Optional Programming Instructions                       | 45 |

| Figure 43: | Optional Program Control and Security Instructions      | 46 |

| Figure 44: | Optional Address and Data Access Instructions           | 46 |

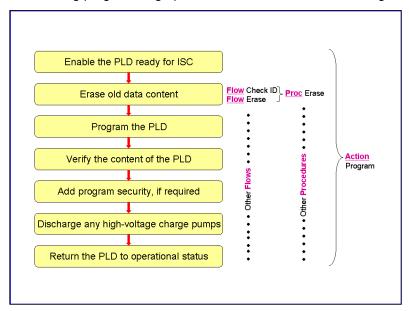

| Figure 45: | Top-Level ISC Programming Flows, Procedures and Actions | 47 |

| Figure 46: | IEEE 1532 - To Probe Further                            | 48 |

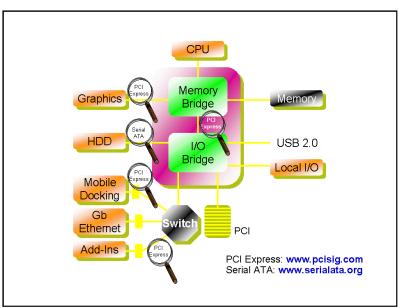

| Figure 47: | High-Speed Serial Buses - Application to PC Motherboard | 49 |

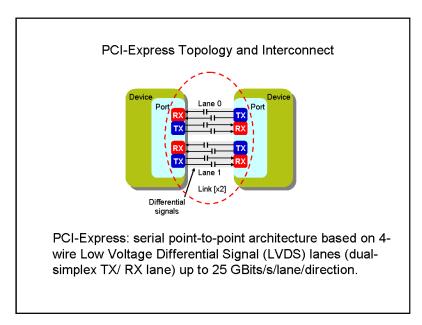

| Figure 48: | PCI-Express Lane Architecture                           | 50 |

| -          | Differential DC Coupling                                |    |

| Figure 50: | Differential AC Coupling                                | 51 |

|            | AC-Coupled SERDES Interconnects                         |    |

| Figure 52: | Where Can Defects Occur?                                | 52 |

| Figure 53: | Options for Testing AC-Coupled Interconnects            | 53 |

| Figure 54: | Interconnect Test: IEEE 1149.6 Solution                 | 54 |

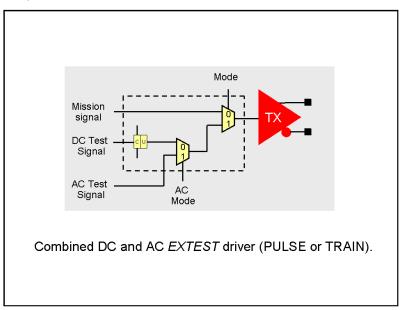

| Figure 55: | Modified TX Boundary-Scan Cell                          | 54 |

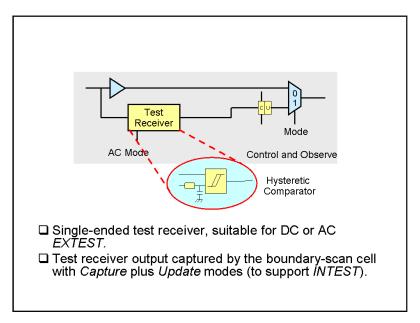

| Figure 56: | 1149.6 Test Receiver                                    | 55 |

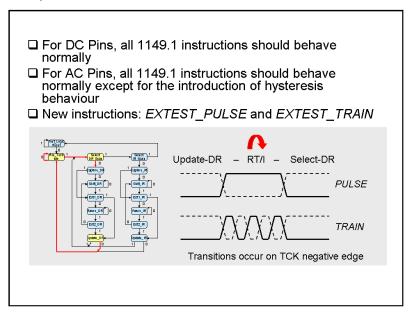

| Figure 57: | New 1149.6 Instructions                                 | 55 |

| •          | IEEE 1149.6 - To Probe Further                          |    |

| Figure 59: | Why Do We Need DFT Guidelines?                          | 57 |

| Figure 60: | ASIC/SoC/SiP Chip-Level DFT Guidelines                  | 58 |

| Figure 61: | Chip-Level DFT Guidelines: Some Examples                | 58 |

| Figure 62: | Chip-Level DFT Guidelines - Some More Examples          | 59 |

| Figure 63: | Board-Level DFT Guidelines                              | 60 |

| Figure 64: | Board-Level DFT Guidelines - Some Examples              | 60 |

| Figure 65: | Board-Level DFT Guidelines - Some More Examples         | 61 |

| •          | Board-Level DFT Guidelines - Yet More Examples          |    |

| Figure 67: | DFT Guidelines - To Probe Further                       | 62 |

| •          | TAP Access to Embedded Instruments                      |    |

| _          | Benchtop + In-Circuit Testers                           |    |

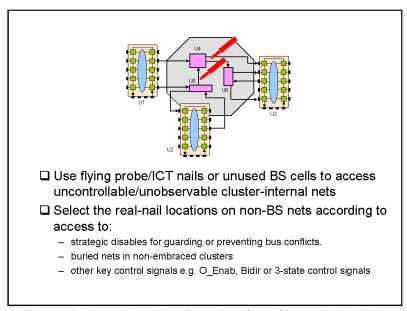

| Figure 70: | Accessing a Non-Boundary-Scan Cluster Using Nails       | 70 |

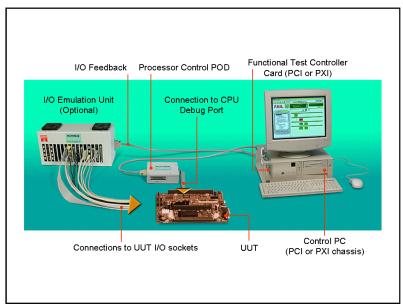

| Figure 71: CPU Emulator Components                           | . 71 |

|--------------------------------------------------------------|------|

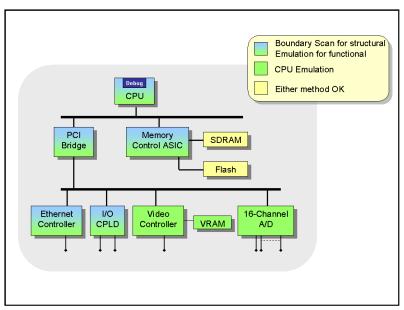

| Figure 72: Boundary Scan and Emulation Dual-Approach Testing | 71   |

| Figure 73: The Explosive Growth of Boundary-Scan Technology  | 72   |

#### Introduction

In this tutorial, you will learn the basic elements of boundary-scan architecture — where it came from, what problems it solves, and its implications on the design of an integrated-circuit device. This tutorial also provides an overview of the data standards applicable to the boundary-scan architecture and an overview of the software tools available to perform boundary-scan-based tests.

The core reference is the 2001 version of the Standard:

IEEE Standard 1149.1-2001 "Test Access Port and Boundary-Scan Architecture," available from the IEEE, 445 Hoes Lane, PO Box 1331, Piscataway, New Jersey 08855-1331, USA.

The standard was initially created in 1990 and revised in 1993, 1994 and 2001. You can obtain a copy of the standard via: http://standards.ieee.org/

For further, more recent publications on the boundary-scan architecture, see the Bibliography at the end of this tutorial.

# **Chapter 1: The Motivation for Boundary-Scan Architecture**

Since the mid-1970s, the structural testing of loaded printed circuit boards (PCBs) has relied very heavily on the use of the so-called in-circuit "bed-of-nails" technique (Figure 1). This method of testing makes use of a fixture containing a bed-of-nails to access individual devices on the board through test landing sites or pads laid into the copper interconnect, or other convenient contact points. Testing then proceeds in two phases: power-off tests followed by power-on tests. Power-off tests check the integrity of the physical contact between a nail and the on-board access point. Open and shorts tests are then carried out based on impedance measurements.

Figure 1: ICT versus Functional Test

Power-on tests apply stimulus to a chosen device on a board, with an accompanying measurement of the response from that device. Other devices that are electrically connected to the device-under-test are usually placed into a safe state (a process called "guarding"). In this way, the tester is able to check the presence, orientation, and bonding of the device-under-test on the board.

Fundamentally, the in-circuit bed-of-nails technique relies on physical access to all devices on a board. For plated-through-hole technology, the access is usually gained by adding test landing sites or "lands" into the interconnects on the "B" side of the board — that is, the solder side of the board. The advent of onserted devices (surface mount) meant that manufacturers began to place components on both sides of the board — the "A" side and the "B" side. The smaller pitch between the leads of surface-mount components caused a corresponding decrease in the physical distance between the interconnects. This had serious impact on the ability to place a nail accurately onto a target test land. The whole question of access was further compounded by the development of multi-layer boards.

Such was the situation in the mid-1980s when a group of concerned test engineers in a number of European electronics systems companies got together to examine the problem and its possible solutions. This group of people called itself the Joint European Test Action Group (JETAG). Their preferred method of solution was based on the concept of a serial shift register around the boundary of the device — hence, the name "boundary scan." Later, the group was joined by representatives from North American companies and the 'E' for "European" was dropped from the title of the organization, leaving it Joint Test Action Group (JTAG). This was the organization that finally converted its ideas into an international standard.

# Chapter 2: The Principle of Boundary-Scan Architecture

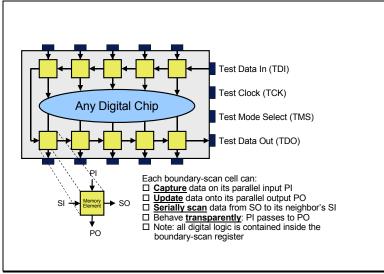

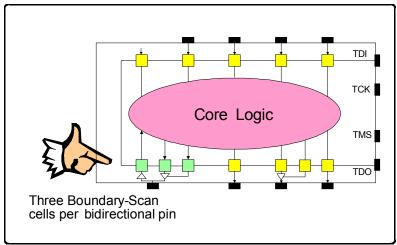

Each primary input signal and primary output signal is supplemented with a multi-purpose memory element called a boundary-scan cell. Cells on a device's primary inputs are referred to as "input cells;" cells on primary outputs are referred to as "output cells." "Input" and "output" is relative to the core logic of the device. (Later, we will see that it is more convenient to reference the terms "input" and "output" to the interconnect between two or more devices.) See Figure 2.

Figure 2: Principle of Boundary-Scan Architecture

The collection of boundary-scan cells is configured into a parallel-in, parallel-out shift register. A parallel load operation, called a "capture" operation, causes signal values on device input pins to be loaded into input cells and signal values passing from the core logic to device output pins to be loaded into output cells. A parallel unload operation — called an "update" operation — causes signal values already present in the output scan cells to be passed out through the device output pins. Depending on the nature of the input scan cells, signal values already present in the input scan cells will be passed into the core logic.

Data can also be shifted around the shift register in serial mode, starting from a dedicated device input pin called "Test Data In" (TDI) and terminating at a dedicated device output pin called "Test Data Out" (TDO). The test clock, TCK, is fed in via yet another dedicated device input pin and the mode of operation is controlled by a dedicated "Test Mode Select" (TMS) serial control signal.

## Using the Scan Path

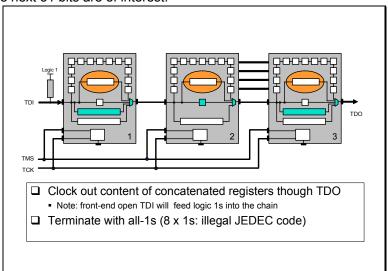

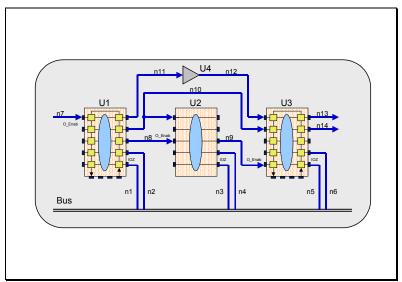

At the device level, the boundary-scan elements contribute nothing to the functionality of the core logic. In fact, the boundary-scan path is independent of the function of the device. As shown in Figure 3, the value of the scan path is at the board level.

Figure 3: Using the Boundary-Scan Path

Figure 3 shows a board containing four boundary-scan devices. Notice that there is an edge-connector input called TDI connected to the TDI of the first device. TDO from the first device is connected to TDI of the second device, and so on, creating a global scan path terminating at the edge connector output called TDO. TCK is connected in parallel to each device's TCK input. TMS works similarly.

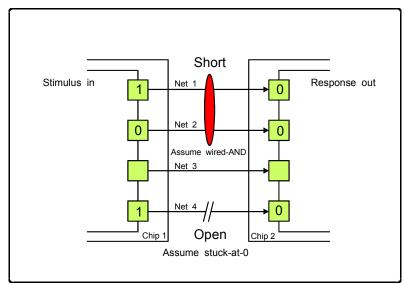

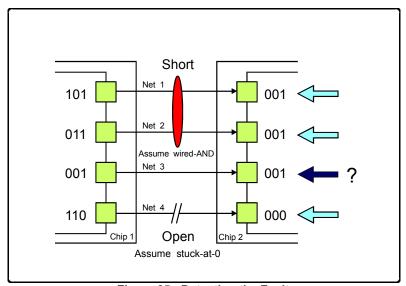

In this way, particular tests can be applied to the device interconnects via the global scan path — by loading the stimulus values into the appropriate device-output scan cells via the edge connector TDI (shift-in operation), applying the stimulus (update operation), capturing the responses at device-input scan cells (capture operation), and shifting the response values out to the edge connector TDO (shift-out operation).

Essentially, boundary-scan cells can be thought of as "virtual nails."

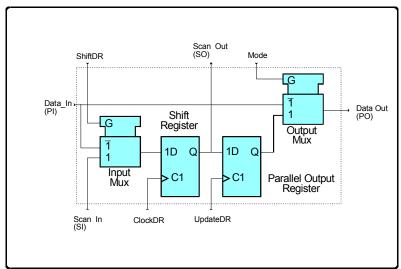

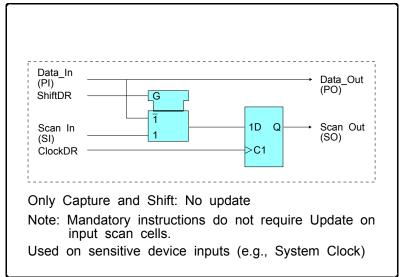

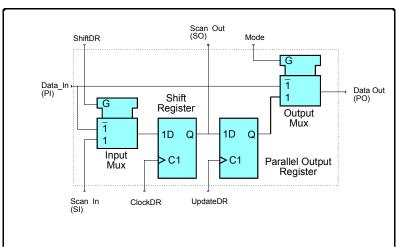

Figure 4 shows a basic universal boundary-scan cell. It has four modes of operation: normal, update, capture, and serial shift. The memory element is shown to be a simple D-type flip-flop with front-end and back-end multiplexing of data. (As with all circuits in this tutorial, it is important to note that the circuit shown in Figure 4 is only an example of how the requirement defined in the Standard could be realized. The IEEE 1149.1 Standard does not mandate the design of the circuit, only its functional specification.)

Figure 4: Basic Boundary-Scan Cell

During normal mode, Data\_In is passed straight through to Data\_Out. During update mode, the content of the output register is passed through to Data\_Out. During capture mode, the Data\_In signal is routed to the shift register and the value is captured by the next ClockDR. During shift mode, the Scan\_Out of one register flip-flop is passed to the Scan\_In of the next via a hard-wired path. Note that both capture and shift operations do not interfere with the normal passing of data from the parallel-in terminal to the parallel-out terminal. This allows the capture of operational values "on the fly" and the movement of these values for inspection without interference with functional modes of operation. This application of the boundary-scan architecture has tremendous potential for real-time monitoring of the operational status of a system — a sort of electronic camera taking snapshots — and is one reason why TCK is kept separate from any system clocks.

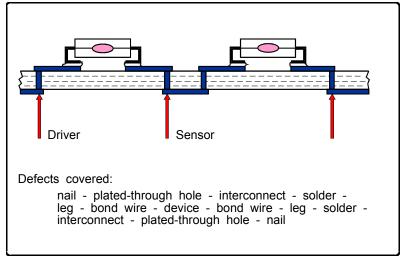

The use of boundary-scan cells to test the presence, orientation, and bonding of devices in place on a circuit board was the original motivation for inclusion in a device. The use of scan cells as a means of applying tests to individual devices is not the major application of boundary-scan architecture. Consider the reasons for boundary-scan architecture in the first place. The prime function of the bed-of-nails in-circuit tester was to test for manufacturing defects, such as missing devices, damaged devices, open and short circuits, misaligned devices, and wrong devices. See Figure 5.

Figure 5: Bed-of-Nails Fault Coverage

In-circuit testers were not intended to prove the overall functionality of the devices on-board. It was assumed that devices had already been tested for functionality prior to assembly on the board. Unfortunately, in-circuit test techniques had to make use of device functionality in order to test the interconnect structure — hence the rather large libraries of merchant device functions and the problems caused by the increasing use of custom designs such as ASICs and cPLDs.

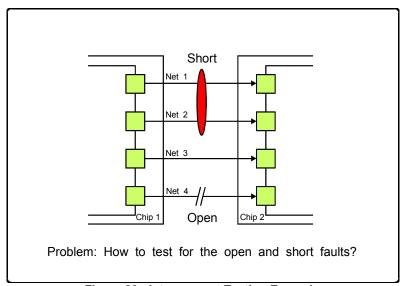

Given that the boundary-scan architecture was seen as an alternative way of testing for the presence of manufacturing defects, we should question what these defects are, what causes them, and where they occur.

An examination of the root cause for defects shows them to be caused by any one of three "shock waves": electrical shock (e.g., electrostatic discharge), mechanical shock (e.g., clumsy handling), or thermal shock (e.g., hot spots caused by the solder operation). A defect, if it occurs, is likely present either in the periphery of the device (leg, bond wire, driver amplifier), in the solder, or in the interconnect between devices. It is very unusual to find damage to the core logic without some sort of associated damage to the periphery of the device.

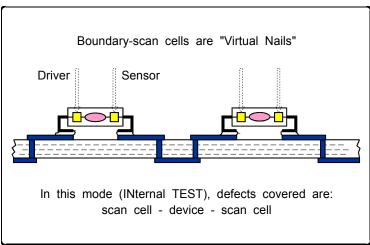

In this respect, the boundary-scan cells are precisely where we want them — at the beginning and ends of the core function of the device (see Figure 6).

Figure 6: Boundary-Scan Fault Coverage (Intest)

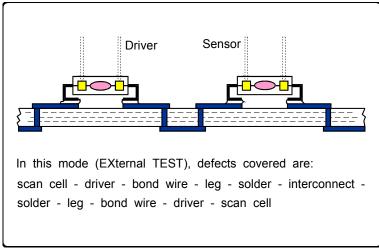

And, more importantly, boundary scan cells are located at the beginning and end of interconnect paths because this is the region most likely to be damaged during board assembly (see Figure 7).

Figure 7: Boundary-Scan Fault Coverage (Extest)

Using boundary-scan cells to test a device's core functionality is called "internal test" or simply *Intest*. Using the boundary-scan cells to test the interconnect structure between two devices is called "external test" or simply *Extest*. The use of the cells for *Extest* is the major application of boundary-scan architecture, searching for opens and shorts plus damage to the periphery of the device. *Intest* is only really used for very limited testing of the core functionality (i.e., an existence test — "are you there, are you alive?") or to identify defects such as devices missing, incorrectly oriented, or misalignment.

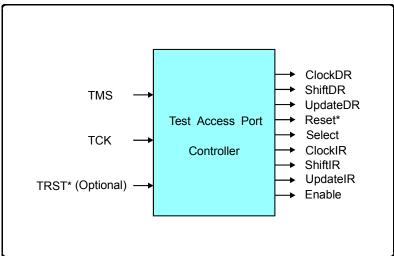

# **Chapter 3: IEEE 1149.1 Device Architecture**

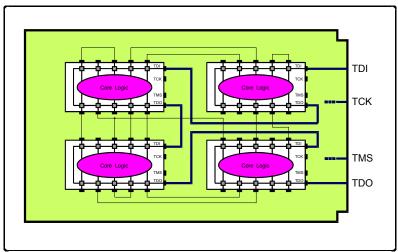

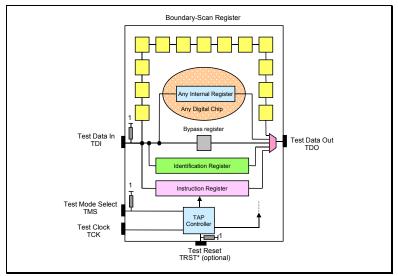

After nearly five years of discussion, the JTAG organization finally proposed the architecture shown in Figure 8.

Figure 8: IEEE 1149.1 Chip Architecture

Figure 8 shows the following elements:

- □ A set of four dedicated test pins Test Data In (TDI), Test Mode Select (TMS), Test Clock (TCK), Test Data Out (TDO) and one optional test pin Test Reset (TRST\*). These pins are collectively referred to as the Test Access Port (TAP).

- □ A boundary-scan cell on the device primary input and primary output pins of a device, connected internally to form a serial boundary-scan register (Boundary Scan).

- □ A finite-state machine TAP controller with inputs TCK, TMS, and TRST\*.

- $\square$  An n-bit (n  $\ge$  2) Instruction Register (IR), holding the current instruction.

- □ A 1-bit bypass register (Bypass).

- An optional 32-bit Identification Register (Ident) capable of being loaded with a permanent device identification code.

At any time, only one register can be connected from TDI to TDO (e.g., IR, Bypass, Boundary-scan, Ident, or even some appropriate register internal to the core logic). The selected register is identified by the decoded output of the IR. Certain instructions are mandatory, such as *Extest* (boundary-scan register selected), whereas others are optional, such as the *Idcode* instruction (Ident register selected).

Let's take a closer look at each part of this architecture.

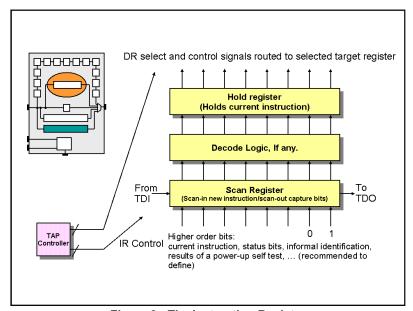

#### The Instruction Register

An Instruction Register (IR) has a shift section that can be connected to TDI and TDO, and a hold section, holding the current instruction as shown in Figure 9.

Figure 9: The Instruction Register

There may be some decoding logic between the two sections depending on the width of the register and the number of different instructions. The control signals to the IR originate from the TAP controller and either cause a shift-in, shift-out through the IR shift section, or cause the contents of the shift section to be passed across to the hold section (update operation). It is also possible to load (capture) certain hard-wired values into the shift section of the IR. The IR must be at least two-bits long (to allow coding of the four mandatory instructions — *Bypass*, *Sample, Preload, Extest* — but the maximum length of the IR is not defined. In capture mode, the two least significant bits must capture a 01 pattern (see Figure 9). The values captured into higher-order bits are not defined. One possible use of these higher order bits is to capture an informal identification code if the 32-bit Ident register is not implemented. In practice, the only mandated bit pattern for IR capture is the 01 pattern. We will return to the value of capturing this pattern later in this tutorial.

# The Instructions

The IEEE 1149.1-2001 version of the Standard describes four mandatory instructions: *Bypass*, *Sample*, *Preload*, and *Extest*.

The *Bypass* instruction must be assigned an all-1s code. When executed, the Bypass instruction causes the Bypass register to be placed between the TDI and TDO pins. By definition, the initialized state of the hold section of the IR should contain the *Bypass* instruction code unless the optional Identification Register (Ident) has been implemented, in which case, the *Idcode* instruction code should be present in the hold section.

The Sample and Preload instructions both select the boundary-scan register when executed. The Sample instruction sets up the boundary-scan cells to sample (capture) values moving into the device. The Preload instruction is used to preload known values into the output boundary-scan cells prior to some follow-on operation. The codes for the Sample and Preload instructions are not defined.

The *Extest* instruction selects the boundary-scan register preparatory to interconnect testing. Prior to the 2001 version of the Standard, the code for *Extest* was defined to be the all-0s code. Since 2001, the code is no longer defined.

The IEEE 1149.1 Standard defines a number of optional instructions (instructions that do not need to be implemented, but which have a prescribed operation when they are used). Examples of optional instructions include:

Intest, the instruction that selects the boundary-scan register preparatory to applying tests to the core logic of the device.

Idcode, the instruction that selects the Identification Register between TDI and TDO preparatory to loading the internal hard-wired Idcode values and reading them out through TDO. Note that if the Idcode instruction is loaded and there is no Identification Register present on the device, then the *Idcode* instruction must be interpreted as if it were the Bypass instruction.

The *Runbist* instruction initiates an internal self-test routine and places the pass/fail result register between TDI and TDO.

Two new instructions were introduced in the 1993 revision, 1149.1a. These were *Clamp* and *Highz*. *Clamp* is an instruction that drives preset scan-cell values onto the outputs of devices (established initially with the Preload instruction) and then selects the Bypass register between TDI and TDO. Clamp would be used to set up safe "guarding" values on the outputs of certain devices in order to avoid bus contention problems, for example.

Highz is similar to Clamp, but the device is designed such that all outputs can be placed in either a high-Z mode (3-state outputs) or input receive mode (for bidirectional scan cells). HighZ establishes these values on the output pins but leaves the Bypass register as the selected register Note that the Enable control signal to do this is supplied directly from the IR upon execution of the HighZ instruction. Preload is not used.

With the exception of Bypass, the codes for all instructions are undefined. Given the need for four mandatory instructions, the minimum length of the IR is two bits. The maximum length is undefined. Any instruction can have more than one code and all unused codes are interpreted as Bypass. Note that the designer may use certain codes to implement "private" instructions — that is, instructions whose functions are not made public. In these circumstances, the designer must state that these codes are private so that the user can avoid loading the codes.

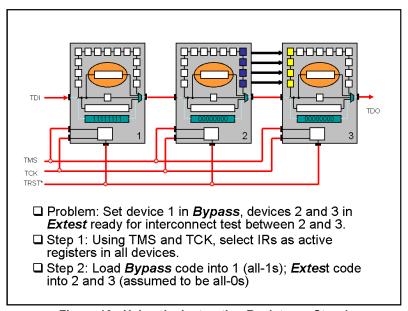

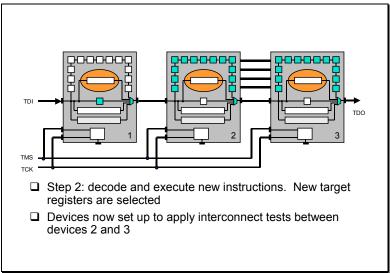

## Using the Instruction Register (IR)

Before proceeding with a description of other parts of the architecture, we will first examine how to load the IR and decode its contents. Consider the board circuit shown in Figure 10.

Figure 10: Using the Instruction Register — Step 1